Los avances y progresos en la tecnología de semiconductores, han reducido las diferencias en las velocidades de procesamiento de los microprocesadores con las velocidades de las memorias, lo que ha repercutido en nuevas tecnologías en el desarrollo de microprocesadores. Hay quienes consideran que en breve los microprocesadores RISC (reduced instruction set computer) sustituirán a los CISC (complex instruction set computer), pero existe el hecho que los microprocesadores CISC tienen un mercado de software muy difundido, aunque tampoco tendrán ya que establecer nuevas familias en comparación con el desarrollo de nuevos proyectos con tecnología RISC.

La arquitectura RISC plantea en su filosofía de diseño una relación muy estrecha entre los compiladores y la misma arquitectura como se verá más adelante.

INTRODUCCIÓN:

Veamos primero cual es el significado de los términos CISC y RISC:

CISC (complex instruction set computer) Computadoras con un conjunto de instrucciones complejo.

RISC (reduced instruction set computer) Computadoras con un conjunto de instrucciones reducido.

Los atributos complejo y reducido describen las diferencias entre los dos modelos de arquitectura para microprocesadores solo de forma superficial. Se requiere de muchas otras características esenciales para definir los RISC y los CISC típicos. Aun más, existen diversos procesadores que no se pueden asignar con facilidad a ninguna categoría determinada.

Así, los términos complejo y reducido, expresan muy bien una importante característica definitiva, siempre que no se tomen solo como referencia las instrucciones, sino que se considere también la complejidad del hardware del procesador.

Con tecnologías de semiconductores comparables e igual frecuencia de reloj, un procesador RISC típico tiene una capacidad de procesamiento de dos a cuatro veces mayor que la de un CISC, pero su estructura de hardware es tan simple, que se puede realizar en una fracción de la superficie ocupada por el circuito integrado de un procesador CISC.

Esto hace suponer que RISC reemplazará al CISC, pero la respuesta a esta cuestión no es tan simple ya que:

Para aplicar una determinada arquitectura de microprocesador son decisivas las condiciones de realización técnica y sobre todo la rentabilidad, incluyendo los costos de software.

Existían y existen razones de compatibilidad para desarrollar y utilizar procesadores de estructura compleja así como un extenso conjunto de instrucciones.

La meta principal es incrementar el rendimiento del procesador, ya sea optimizando alguno existente o se desee crear uno nuevo. Para esto se deben considerar tres áreas principales a cubrir en el diseño del procesador y estas son:

- La arquitectura.

- La tecnología de proceso.

- El encapsulado.

La tecnología de proceso, se refiere a los materiales y técnicas utilizadas en la fabricación del circuito integrado, el encapsulado se refiere a cómo se integra un procesador con lo que lo rodea en un sistema funcional, que de alguna manera determina la velocidad total del sistema.

Aunque la tecnología de proceso y de encapsulado son vitales en la elaboración de procesadores más rápidos, es la arquitectura del procesador lo que hace la diferencia entre el rendimiento de una CPU (Control Process Unit) y otra. Y es en la evaluación de las arquítecturas RISC y CISC donde centraremos nuestra atención.

Dependiendo de cómo el procesador almacena los operandos de las instrucciones de la CPU, existen tres tipos de juegos de instrucciones:

- Juego de instrucciones para arquitecturas basadas en pilas.

- Juego de instrucciones para arquitecturas basadas en acumulador.

- Juego de instrucciones para arquitecturas basadas en registros.

Las arquítecturas RISC y CISC son ejemplos de CPU con un conjunto de instrucciones para arquítecturas basadas en registros.

ARQUITECTURAS CISC:

La microprogramación es una característica importante y esencial de casi todas las arquítecturas CISC.

Como por ejemplo:

Intel 8086, 8088, 80286, 80386, 80486.

Motorola 68000, 68010, 68020, 68030, 6840.

La microprogramación significa que cada instrucción de máquina es interpretada por un microprograma localizado en una memoria en el circuito integrado del procesador.

En la década de los sesentas la micropramación, por sus características, era la técnica más apropiada para las tecnologías de memorias existentes en esa época y permitía desarrollar también procesadores con compatibilidad ascendente. En consecuencia, los procesadores se dotaron de poderosos conjuntos de instrucciones.

Las instrucciones compuestas son decodificadas internamente y ejecutadas con una serie de microinstrucciones almacenadas en una ROM interna. Para esto se requieren de varios ciclos de reloj (al menos uno por microinstrucción).

ARQUITECTURAS RISC:

Buscando aumentar la velocidad del procesamiento se descubrió en base a experimentos que, con una determinada arquitectura de base, la ejecución de programas compilados directamente con microinstrucciones y residentes en memoria externa al circuito integrado resultaban ser mas eficientes, gracias a que el tiempo de acceso de las memorias se fue decrementando conforme se mejoraba su tecnología de encapsulado.

Debido a que se tiene un conjunto de instrucciones simplificado, éstas se pueden implantar por hardware directamente en la CPU, lo cual elimina el microcódigo y la necesidad de decodificar instrucciones complejas.

En investigaciones hechas a mediados de la década de los setentas, con respecto a la frecuencia de utilización de una instrucción en un CISC y al tiempo para su ejecución, se observó lo siguiente:

- Alrededor del 20% de las instrucciones ocupa el 80% del tiempo total de ejecución de un programa.

- Existen secuencias de instrucciones simples que obtienen el mismo resultado que secuencias complejas predeterminadas, pero requieren tiempos de ejecución más cortos.

Las características esenciales de una arquitectura RISC pueden resumirse como sigue:

Estos microprocesadores siguen tomando como base el esquema moderno de Von Neumann.

Las instrucciones, aunque con otras características, siguen divididas en tres grupos:

a) Transferencia.

b) Operaciones.

c) Control de flujo.

Reducción del conjunto de instrucciones a instrucciones básicas simples, con la que pueden implantarse todas las operaciones complejas.

Arquitectura del tipo load-store (carga y almacena). Las únicas instrucciones que tienen acceso a la memoria son 'load' y 'store'; registro a registro, con un menor número de acceso a memoria.

Casi todas las instrucciones pueden ejecutarse dentro de un ciclo de reloj. Con un control implantado por hardware (con un diseño del tipo load-store), casi todas las instrucciones se pueden ejecutar cada ciclo de reloj, base importante para la reorganización de la ejecución de instrucciones por medio de un compilador.

Pipeline (ejecución simultánea de varias instrucciones). Posibilidad de reducir el número de ciclos de máquina necesarios para la ejecución de la instrucción, ya que esta técnica permite que una instrucción puede empezar a ejecutarse antes de que haya terminado la anterior.

El hecho de que la estructura simple de un procesador RISC conduzca a una notable reducción de la superficie del circuito integrado, se aprovecha con frecuencia para ubicar en el mismo, funciones adicionales:

Unidad para el procesamiento aritmético de punto flotante.

Unidad de administración de memoria.

Funciones de control de memoria cache.

Implantación de un conjunto de registros múltiples.

La relativa sencillez de la arquitectura de los procesadores RISC conduce a ciclos de diseño más cortos cuando se desarrollan nuevas versiones, lo que posibilita siempre la aplicación de las más recientes tecnologías de semiconductores. Por ello, los procesadores RISC no solo tienden a ofrecer una capacidad de procesamiento del sistema de 2 a 4 veces mayor, sino que los saltos de capacidad que se producen de generación en generación son mucho mayores que en los CISC.

Por otra parte, es necesario considerar también que:

La disponibilidad de memorias grandes, baratas y con tiempos de acceso menores de 60 ns en tecnologías CMOS.

Módulos SRAM (Memoria de acceso aleatorio estática) para memorias cache con tiempos de acceso menores a los 15 ns.

Tecnologías de encapsulado que permiten realizar más de 120 terminales.

Esto ha hecho cambiar, en la segunda mitad de la década de los ochentas, esencialmente las condiciones técnicas para arquítecturas RISC.

La siguiente tabla esquematiza algunas de las principales características de las arquitecturas RISC Y CISC.

PRINCIPIOS DE DISEÑO DE LAS MAQUINAS RISC

Resulta un tanto ingenuo querer abarcar completamente los principios de diseño de las máquinas RISC, sin embargo, se intentará presentar de una manera general la filosofía básica de diseño de estas maquinas, teniendo en cuenta que dicha filosofía puede presentar variantes. Es muy importante conocer estos principios básicos, pues de éstos se desprenden algunas características importantes de los sistemas basados en microprocesadores RISC.

En el diseño de una máquina RISC se tienen cinco pasos:

Analizar las aplicaciones para encontrar las operaciones clave.

Diseñar un bus de datos que sea óptimo para las operaciones clave.

Diseñar instrucciones que realicen las operaciones clave utilizando el bus de datos.

Agregar nuevas instrucciones sólo si no hacen más lenta a la máquina.

Repetir este proceso para otros recursos.

El primer punto se refiere a que el diseñador deberá encontrar qué es lo que hacen en realidad los programas que se pretenden ejecutar. Ya sea que los programas a ejecutar sean del tipo algorítmicos tradicionales, o estén dirigidos a robótica o al diseño asistido por computadora.

La parte medular de cualquier sistema es la que contiene los registros, el ALU y los 'buses' que los conectan. Se debe optimar este circuito para el lenguaje o aplicación en cuestión. El tiempo requerido, (denominado tiempo del ciclo del bus de datos) para extraer los operandos de sus registros, mover los datos a través del ALU y almacenar el resultado de nuevo en un registro, deberá hacerse en el tiempo mas corto posible.

El siguiente punto a cubrir es diseñar instrucciones de máquina que hagan un buen uso del bus de datos. Por lo general se necesitan solo unas cuantas instrucciones y modos de direccionamiento; sólo se deben colocar instrucciones adicionales si serán usadas con frecuencia y no reducen el desempeño de las más importantes.

Siempre que aparezca una nueva y atractiva característica, deberá analizarse y ver la forma en que se afecta al ciclo de bus. Si se incrementa el tiempo del ciclo, probablemente no vale la pena tenerla.

Por último, el proceso anterior debe repetirse para otros recursos dentro del sistema, tales como memoria cache, administración de memoria, coprocesadores de punto flotante, etcétera.

Una vez planteadas las características principales de la arquitectura RISC así como la filosofía de su diseño, podríamos extender el análisis y estudio de cada una de las características importantes de las arquítecturas RISC y las implicaciones que estas tienen.

PAPEL DE LOS COMPILADORES EN UN SISTEMA RISC:

El compilador juega un papel clave para un sistema RISC equilibrado.

Todas las operaciones complejas se trasladan al microprocesador por medio de conexiones fijas en el circuito integrado para agilizar las instrucciones básicas más importantes. De esta manera, el compilador asume la función de un mediador inteligente entre el programa de aplicación y el microprocesador. Es decir, se hace un gran esfuerzo para mantener al hardware tan simple como sea posible, aún a costa de hacer al compilador considerablemente más complicado. Esta estrategia se encuentra en clara contra posición con las máquinas CISC que tienen modos de direccionamiento muy complicados. En la práctica, la existencia en algunos modos de direccionamiento complicados en los microprocesadores CISC, hacen que tanto el compilador como el microprograma sean muy complicados.

No obstante, las máquinas CISC no tienen características complicadas como carga, almacenamiento y salto que consumen mucho tiempo, las cuales en efecto aumentan la complejidad del compilador.

Para suministrar datos al microprocesador de tal forma que siempre esté trabajando en forma eficiente, se aplican diferentes técnicas de optimización en distintos niveles jerárquicos del software.

Los diseñadores de RISC en la empresa MIP y en Hewlett Packard trabajan según la regla siguiente:

Una instrucción ingresa en forma fija en el circuito integrado del procesador (es decir, se alambra físicamente en el procesador) si se ha demostrado que la capacidad total del sistema se incrementa en por lo menos un 1%.

En cambio, los procesadores CISC, han sido desarrollados por equipos especializados de las empresas productoras de semiconductores y con frecuencia el desarrollo de compiladores se sigue por separado. Por consiguiente, los diseñadores de los compiladores se encuentran con una interfaz hacia el procesador ya definido y no pueden influir sobre la distribución óptima de las funciones entre el procesador y compilador.

Las empresas de software que desarrollan compiladores y programas de aplicación, tienden por razones de rentabilidad, a utilizar diferentes procesadores como usuarios de su software en lugar de realizar una optimización completa, y aprovechar así las respectivas características de cada uno. Lo cual también genera otros factores negativos de eficiencia. Esta limitación de las posibilidades de optimización del sistema, que viene dada a menudo por una obligada compatibilidad, se superó con los modernos desarrollos RISC.

CAPACIDAD DE PROCESAMIENTO DE LOS SISTEMAS DESDE EL PUNTO DE VISTA DEL USUARIO

Aparte de la base conceptual para el desarrollo de un sistema de computación de alta calidad, se requieren técnicas especiales para optimizar cada uno de los factores que determinan la capacidad de procesamiento, la cual, solo puede definirse con el programa de aplicación.

La información suministrada por un fabricante, sobre la velocidad en mips (millones de Instrucciones por segundo) que una arquitectura es capaz de realizar, carece de relevancia hasta que el usuario sepa cuantas instrucciones genera el respectivo compilador, al traducir su programa de aplicación y cuánto tiempo tarda la ejecución de estas instrucciones, y solo el análisis de diferentes pruebas y comparaciones de rendimiento ("benchmarks) da una idea aproximada, que el usuario puede aplicar para delimitar las arquítecturas adecuadas.

Dos diferentes puntos de vista acerca de capacidad de procesamiento del sistema.

Sistema reprogramable. Un usuario que necesite desarrollar un sistema reprogramable, no está interesado en obtener una alta capacidad de procesamiento.

Sistema incluido o dedicado. En estos sistemas el principal objetivo es procesar en forma repetitiva una serie de aplicaciones o funciones determinadas, y es de suma importancia la mayor cantidad posible de pruebas y comparaciones de rendimiento ("benchmarks" ) diferentes.

Así, estas pruebas y comparaciones sirven para determinar la capacidad de procesamiento de los sistemas, pero solo el análisis de varios resultados de diferentes programas da una idea aproximada de la capacidad de procesamiento real.

APLICACIONES DE LOS PROCESADORES RISC

Las arquitecturas CISC utilizadas desde hace 15 años han permitido desarrollar un gran número de productos de software. Ello representa una considerable inversión y asegura a estas familias de procesadores un mercado creciente. Sin embargo, simultáneamente aumentan las aplicaciones en las cuales la capacidad de procesamiento que se pueda obtener del sistema es más importante que la compatibilidad con el hardware y el software anteriores, lo cual no solo es válido en los subsistemas de alta capacidad en el campo de los sistemas llamados "embedded", en los que siempre dominaron las soluciones especiales de alta capacidad de procesamiento sino también para las estaciones de trabajo ("workstations"). Esta clase de equipos se han introducido poco a poco en oficinas, en la medicina y en bancos, debido a los cada vez mas voluminosos y complejos paquetes de software que con sus crecientes requerimientos de reproducción visual, que antes se encontraban solo en el campo técnico de la investigación y desarrollo.

En este tipo de equipos, el software de aplicación, se ejecuta bajo el sistema operativo UNIX, el cual es escrito en lenguaje C, por lo que las arquítecturas RISC actuales están adaptadas y optimizadas para este lenguaje de alto nivel. Por ello, todos los productores de estaciones de trabajo de renombre, han pasado en pocos años, de los procesadores CISC a los RISC, lo cual se refleja en el fuerte incremento anual del número de procesadores RISC, (los procesadores RISC de 32 bits han visto crecer su mercado hasta en un 150% anual). En pocos años, el RISC conquistará de 25 al 30% del mercado de los 32 bits, pese al aparentemente abrumador volumen de software basado en procesadores con el estándar CISC que se ha comercializado en todo el mundo.

La arquitectura MIPS-RISC ha encontrado, en el sector de estaciones de trabajo, la mayor aceptación. Los procesadores MIPS son fabricados y comercializados por cinco empresas productoras de semiconductores, entre las que figuran NEC y Siemens. Los procesadores de los cinco proveedores son compatibles en cuanto a las terminales, las funciones y los bits.

CONCLUSIONES:

Cada usuario debe decidirse a favor o en contra de determinada arquitectura de procesador en función de la aplicación concreta que quiera realizar. Esto vale tanto para la decisión por una determinada arquitectura CISC o RISC, como para determinar si RISC puede emplearse en forma rentable para una aplicación concreta.

Nunca será decisiva únicamente la capacidad de procesamiento del microprocesador, y sí la capacidad real que puede alcanzar el sistema en su conjunto.

Los costos, por su parte, también serán evaluados.

Supongamos por ejemplo, que el precio de un procesador sea de $500.00 USD, éste será secundario para un usuario que diseña una estación de trabajo para venderla después a un precio de $100 000.00 USD. Su decisión se orientará exclusivamente por la potencialidad de este procesador.

RISC ofrece soluciones atractivas donde se requiere una elevada capacidad de procesamiento y se presente una orientación hacia los lenguajes de alto nivel.

En el campo industrial existe un gran número de aplicaciones que ni siquiera agotan las posibilidades de los controladores CISC de 8 bits actuales.

Si bién el campo de aplicaciones de las arquítecturas RISC de alta capacidad crece con fuerza, esto no equivale al fin de otras arquítecturas de procesadores y controladores acreditadas que también seguirán perfeccionándose, lo que si resulta dudoso es la creación de familias CISC completamente nuevas.

Adoptando técnicas típicas de los procesadores RISC en las nuevas versiones de procesadores CISC, se intenta encontrar nuevas rutas para el incremento de la capacidad de las familias CISC ya establecidas.

Entre tanto, los procesadores RISC han conquistado el sector de las estaciones de trabajo, dominado antes por los procesadores Motorola 68 000, y es muy probable que acosen la arquitectura Intel en el sector superior de las PC's.

Las decisiones en el mercado las toman los usuarios, y aquí, el software o la aplicación concreta juega un papel mucho más importante que las diferencias entre las estructuras que son inapreciables para el usuario final.

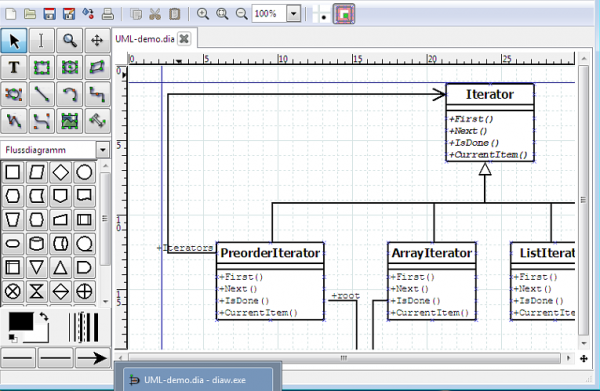

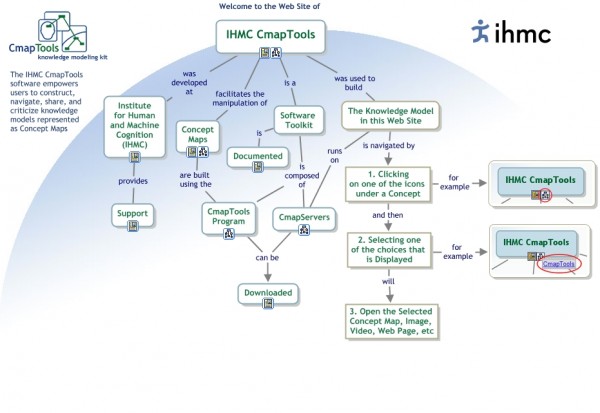

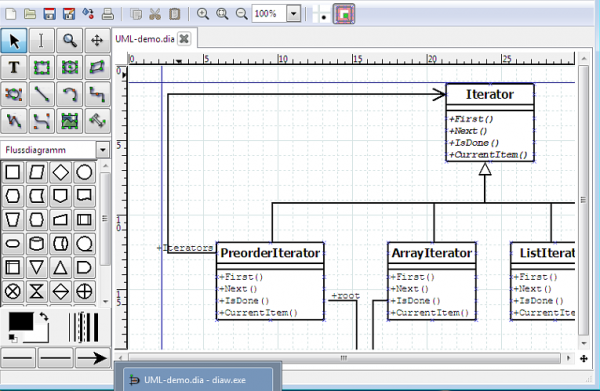

Un aplicación Open Source con un diseño muy intuitivo, iconos grandes, inserción de imágenes y cuadrículas guía en el campo de dibujo. Junto a su formato especial de archivos .dia permite exportar los resultados a los formatos más populares de imágenes y diagramas, incluyendo por supuesto los .vdx de Visio. Funciona en Windows, GNU/Linux y Mac OS X.

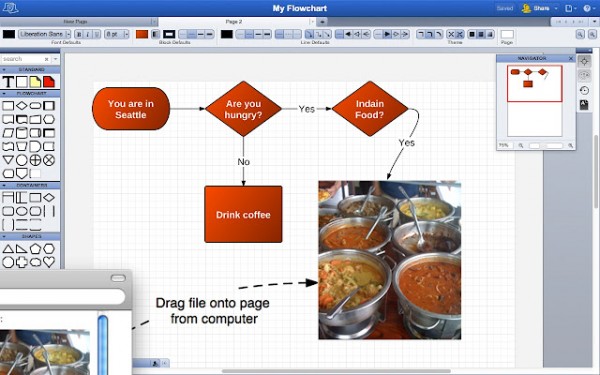

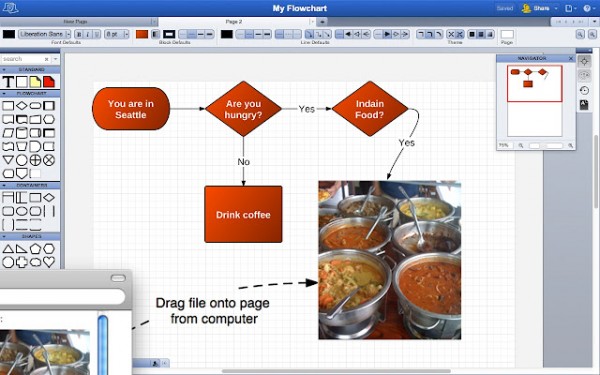

Un aplicación Open Source con un diseño muy intuitivo, iconos grandes, inserción de imágenes y cuadrículas guía en el campo de dibujo. Junto a su formato especial de archivos .dia permite exportar los resultados a los formatos más populares de imágenes y diagramas, incluyendo por supuesto los .vdx de Visio. Funciona en Windows, GNU/Linux y Mac OS X. Una alternativa Online caracterizada por sus opciones de arrastrar y soltar todo tipo de objetos, trabajo colaborativo y un buscador integrado que analiza las bases de datos de Icon Finder y Google Images para disponer de cualquier imagen en la red al instante. El registro es gratuito aunque las funcionalidades extra requieren al menos de cuentas de email .edu.

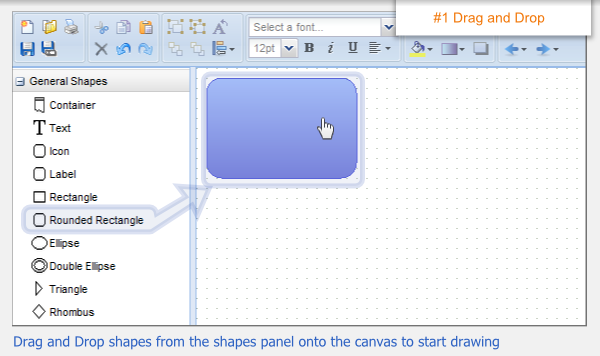

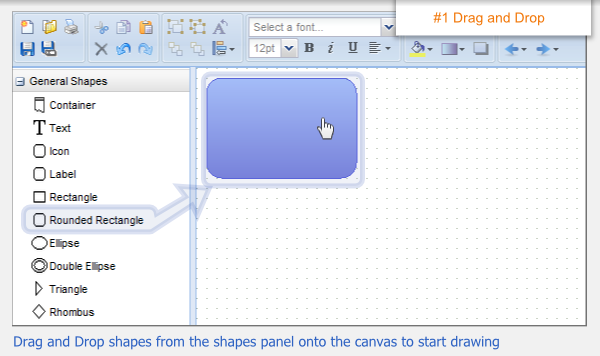

Una alternativa Online caracterizada por sus opciones de arrastrar y soltar todo tipo de objetos, trabajo colaborativo y un buscador integrado que analiza las bases de datos de Icon Finder y Google Images para disponer de cualquier imagen en la red al instante. El registro es gratuito aunque las funcionalidades extra requieren al menos de cuentas de email .edu. También Online, drag and drop, con vista previa de la página completa, menús desplegables al estilo Visio -incluso el color es parecido- y un destacable sistema de organización de elementos por categorías. No tiene siquiera pantalla de inicio o de registro, basta con entrar a la página para ya estar en el campo de dibujo. Los resultados pueden guardarse como XML, PNG, JPG y SVG.

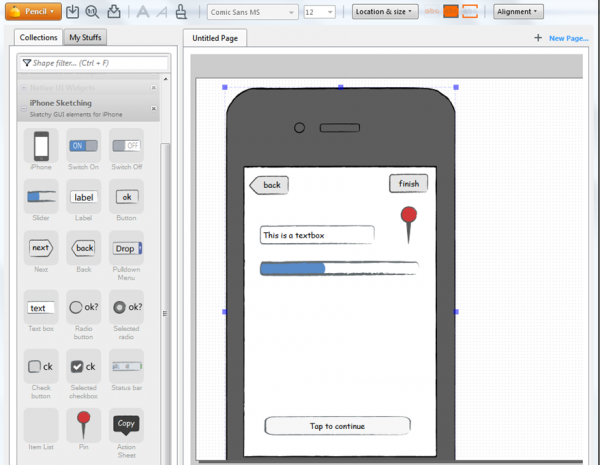

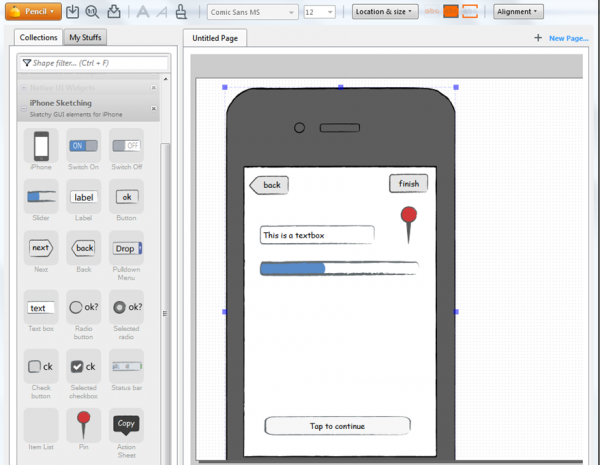

También Online, drag and drop, con vista previa de la página completa, menús desplegables al estilo Visio -incluso el color es parecido- y un destacable sistema de organización de elementos por categorías. No tiene siquiera pantalla de inicio o de registro, basta con entrar a la página para ya estar en el campo de dibujo. Los resultados pueden guardarse como XML, PNG, JPG y SVG. Para diseñar los algoritmos y primeros esquemas de interfaces de aplicaciones (GUI) tanto móviles como para PC, contando para ello con decenas de plantillas predeterminadas según el proyecto. Viene como extensión para Firefox y aplicaciones de escritorio para los OS populares.

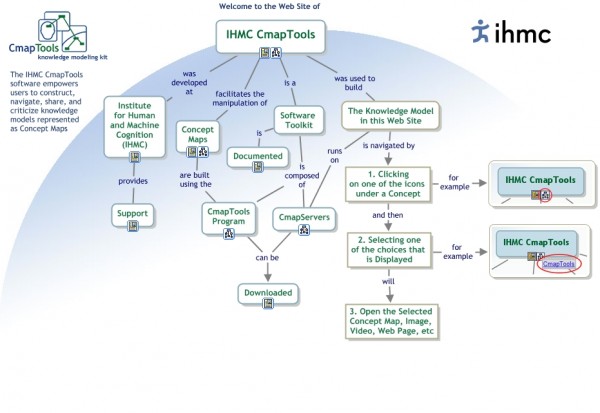

Para diseñar los algoritmos y primeros esquemas de interfaces de aplicaciones (GUI) tanto móviles como para PC, contando para ello con decenas de plantillas predeterminadas según el proyecto. Viene como extensión para Firefox y aplicaciones de escritorio para los OS populares. Brinda la posibilidad de realizar mapas conceptuales apenas arrastrando las formas obteniendo simultáneamente las flechas de unión y campos de texto. Se encuentra limitado por el uso correcto de conectores y conceptos, aunque la gestión de contenidos es impecable. Por defecto sólo funciona en Windows.

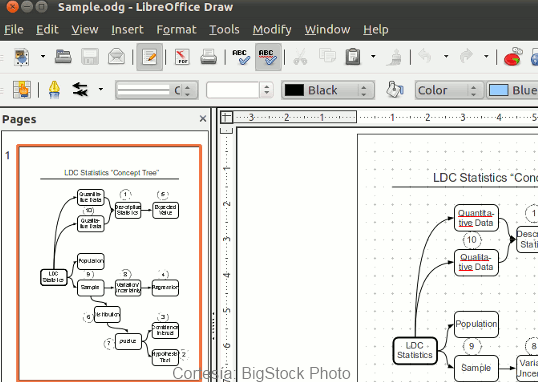

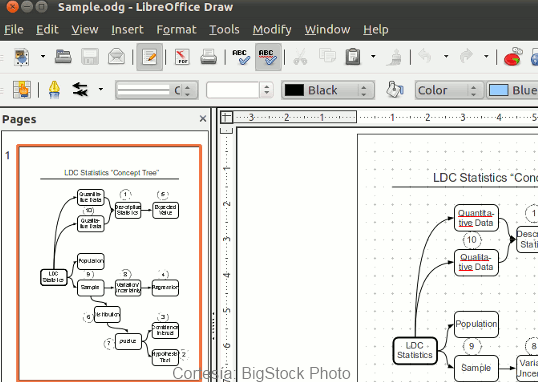

Brinda la posibilidad de realizar mapas conceptuales apenas arrastrando las formas obteniendo simultáneamente las flechas de unión y campos de texto. Se encuentra limitado por el uso correcto de conectores y conceptos, aunque la gestión de contenidos es impecable. Por defecto sólo funciona en Windows. La herramienta de dibujo de las suites ofimáticas libres dispone de una buena cantidad de recursos para realizar diagramas de manera sencilla, además de que su diseño limpio y ligero permite sacar beneficio de todas sus funciones desde el primer uso. Exporta a formatos XML, SWF, PDF e imagen. Me atrevería a decir que la mejor alternativa a Microsoft Visio, especialmente por la cantidad de ayuda en línea para exprimirle aún más y la compatibilidad con el resto de la suite.

La herramienta de dibujo de las suites ofimáticas libres dispone de una buena cantidad de recursos para realizar diagramas de manera sencilla, además de que su diseño limpio y ligero permite sacar beneficio de todas sus funciones desde el primer uso. Exporta a formatos XML, SWF, PDF e imagen. Me atrevería a decir que la mejor alternativa a Microsoft Visio, especialmente por la cantidad de ayuda en línea para exprimirle aún más y la compatibilidad con el resto de la suite.